设计一个简易的处理器(6)--简单的流水线实现PIPE-

上一篇已经介绍了SEQ+的实现,本篇介绍流水线的通用原理及其简单的流水线实现PIPE-.

SEQ/SEQ+的局限性

————

通过前面几篇文章介绍SEQ/SEQ+,不难发现SEQ/SEQ+的一些局限性.

-实际中的SEQ/SEQ+太慢, CPU的时钟太慢,性能太差.

-在每一个时钟周期中,必须更新一条指令的所有可见状态(包括存储器,寄存器文件,条件码和指令寄存器, PC).

-没有充分利用CPU的各个硬件单元(一个时钟周期内只有少量时间硬件单元是活动的).

基于以上几点, SEQ/SEQ+无法达到实际的需求,引入了流水线系统.

流水线的通用原理

————

1.流水线的引入

在设计一个流水线化的处理器之前,先介绍一下流水线化系统的通用原理.实际生产中,流水线的思想经常用于汽车的生产制造,通过将待执行的任务划分为若干个阶段,这样就容许多辆汽车通过生产线的不同阶段,而不用等到一辆汽车生产完成之后再生产下一辆汽车,增加了产能(专业术语:"吞吐量",后面介绍).

假定在一个非流水线化的硬件系统中,如下图所示,该系统由一个执行计算的逻辑和保存计算结果的寄存器构成.

在每个320ps的周期内,系统用300ps(1s=1012ps)计算组合逻辑函数, 20ps用来存储计算结果至寄存器中.

定义延迟(latency)和吞吐量(throughput).

延迟:执行一条指令所需要的时间,称为延迟.

吞吐量:延迟的倒数.

则:吞吐量 = 1/((20+320)*10-12)=3.12*109IPS =3.12GIPS(GIPS: 每秒千兆条指令)

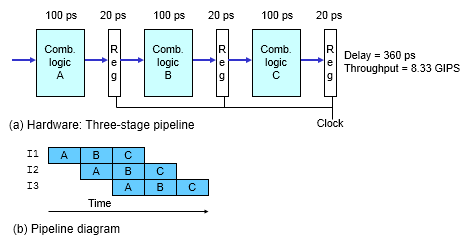

如果将上述系统的执行的计算分为三个阶段A, B, C,每个阶段都为100ps.并且在阶段之间加入流水线寄存器(用来保留的中间结果).如下图所示:

可以知道:吞吐量=1000/(100+20) = 8.33GIPS

2.流水线的优点和局限性

优点-流水线的引入,通过流水线的深度提高了系统的吞吐量,更加了系统的处理性能.

局限性:

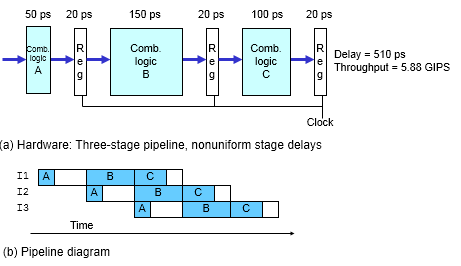

-不一致划分.理想的流水线可以均分,但是现实中往往会不一致的划分.系统的吞吐量受最慢阶段的制约,导致某些阶段并不完全处于活动状态 .

-流水线过深,收益下降.一方面,流水线过深,会导致存储占用时间的比重上升, 导致吞吐量并没有提高多少, 反而增加了延迟,当然硬件成本也上升了.

-现实中,流水线往往带有反馈.需要增加更多的控制逻辑.

流水线技术是典型的空间换时间的技术.现代处理器的流水线很深(15或者更多的阶段),来提高时钟频率(主频).

先睹为快:简单的流水线系统PIPE-

————

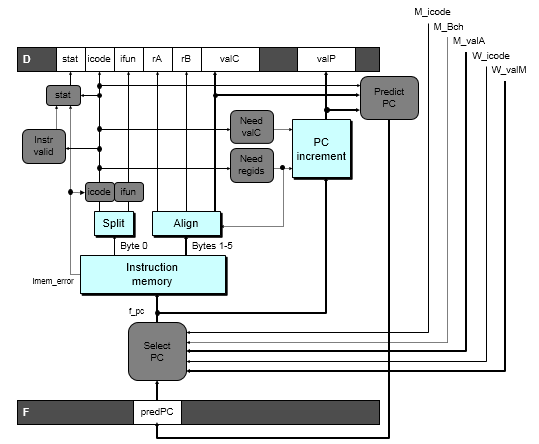

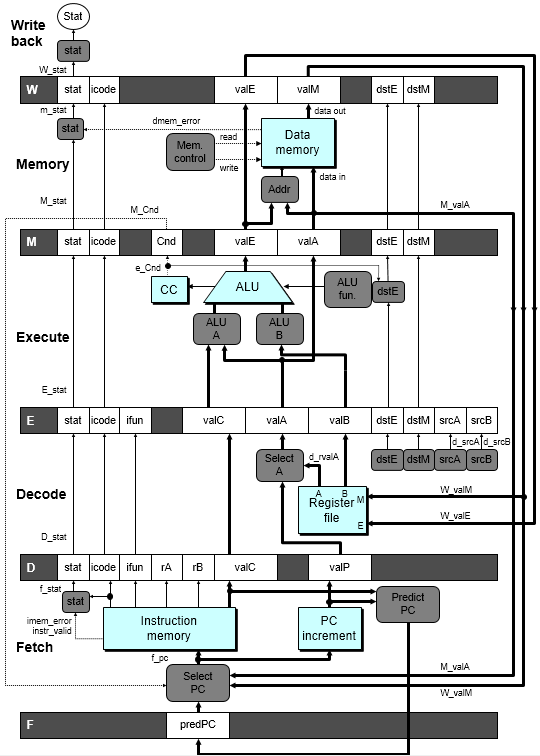

可以在SEQ+的基础上,在各个阶段之间,加上流水线寄存器,改造成PIPE-.先睹为快,稍后分析.

PIPE-的硬件结构

上图说明:

整个硬件框图.实际上大部分内容与SEQ+相同.变化有:

- 信号的重新组织与命名.在原有输入信号前面加上流水线寄存器名称(大写)以区分各自用到的信号,如 D_icode, E_icode, M_icode, and W_icode;如果这些信号是某一阶段产生的,则以小写字母作前缀,如在Execute阶段产生的e_valE信号.

- 在Fetch阶段增加了Predict PC部件来预测下一条指令的地址(后面详细介绍).

- 将valP和valA在Decode阶段合并为一个信号,所以多了一个Select A部件(后面详细介绍).

分析PIPE-

————

1. PIPE-的各个阶段(向上路径)

(1).取指:

-选择当前的PC(因为PC的计算量很小,所以与Fetch合并)

-从存储器中读取指令至指令寄存器.

- PC increment

(2).译码 -读取程序寄存器

(3).执行 - ALU

(4).访存 - Read/Write数据寄存器

(5).写回 -更新程序寄存器文件.

2.PIPE-的反馈路径

仔细观察PIPE-的硬件结构,不难发现有两条反馈路径(介绍控制逻辑的时候纤细介绍).

(1).Selected PC

(2).Register updates

PIPE-的两处重要的变化

————

1. Select A

主要用处是减少控制信号和寄存器的数目.因为只有call指令会在memory阶段用到valP,只有jxx指令会在execute阶段用到valP. 这两种指令都不需要用到寄存器A.所以可以将这两个控制信号合并.

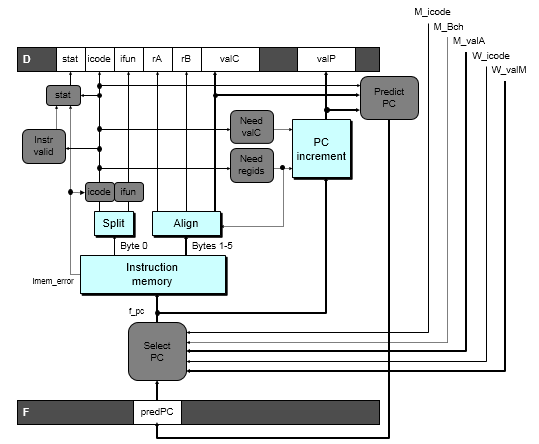

2. Select PC

(1). Predicting PC的理论

流水线系统中,各个硬件单元都得到充分利用,取指模块取完一条指令后,取下一条指令.但是流水线系统中的程序可见的状态是分阶段更新的,导致没有办法在指令刚完成fetch就知道下一条指令在哪里.这就产生了Predicting PC.

Predicting PC包含了两个方面,一个是如何预测PC,另一个是如何从错误的预测中恢复过来.

预测PC有很多种方法,下面介绍PIPE-使用的一种简单的策略.

- 不传递控制的指令.下一条指令始总是valP.

- call/jump.下一条指令总是valC.

- jxx. PIPE-预测下一条指令的位置是valC(60%的正确率).

- ret. PIPE-对ret指令不预测.

我们发现只有jxx和ret的下一条指令时不确定的, PIPE-采用的是一种非常简单的策略,当然有针对jxx和ret的更加优秀的策略,但是无疑增加了控制旁路.

(2). PIPE-的PC的选择和取指逻辑

intF_predPC = [

f_icodein {IJXX, ICALL} : f_valC;

1:f_valP;

];

Select PC的逻辑(注意这是一个反馈路径)

int f_PC = [

#mispredicted branch. Fetch at incremented PC

M_icode== IJXX && !M_Bch : M_valA;

#completionof RET instruciton

W_icode== IRET : W_valM;

#default:Use predicted value of PC

1:F_predPC

];

现有PIPE-的功能和局限性

————

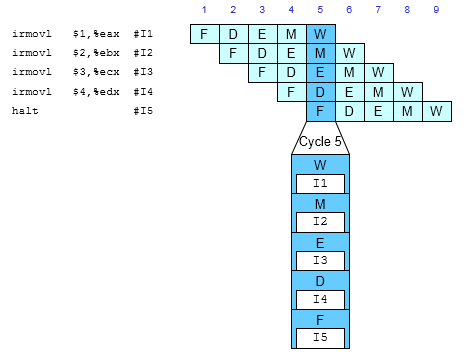

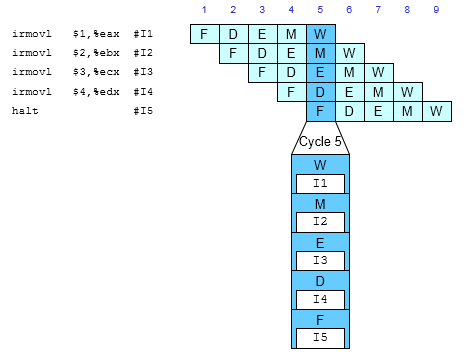

下图是PIPE-的流水线的演示:

这里可以解释一下"为什么我们的各个阶段是自下向上的啦".可以看Cycle5.正好是F-D-E-M-W.

必须要强调一点, PIPE-是有致命缺陷的, PIPE-无法解决数据相关和控制相关的问题.预知后势如何,请看下文分解

注*:本篇中的图片均来自本书的官网,我进行了改造(注释和添加),详见http://csapp.cs.cmu.edu/public/figures.html

(Copyright? 2011, Randal E. Bryant and David R. O'Hallaron )

reference:

1. 深入理解计算机系统(原书第2版)

(版权所有,转载时请注明作者和出处-dennis_fan-http://blog.csdn.net/dennis_fan