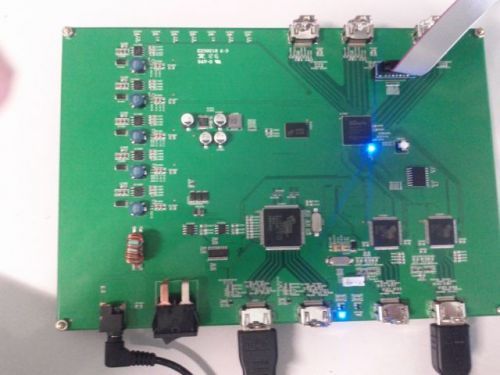

open3D 开发板首次试做成功

经过如此漫长的等待,终于拿到板子了,一共5块,散发着松香的清新味道。

初步测试检查,虔诚的祈祷之后,通电,没有火花....

连接上jtag,能够检测到LX45芯片的信息,心中一阵激动,下载mcs文件,指示灯亮起,电视显示出“AVATAR 3D“字样,这是蓝光碟片上的一个测试场景,激动的发晕.....成功了 。

这次试做的开发板上集成了此前ML605版和atlys版的优点,一共有7个HDMI接口:

2个HDMI ASIC输入,在ML605和Atlys上验证过

2个HDMI ASIC输出,在ML605上验证过

3个 输入/输出均可,在atlys上验证过

在其他设计上,open3D开发板考虑的也很周全的,比如电源,用了5+1路独立供电,每一路都是5V-17V的宽电源设计,这样就不会发生上次俺把atlys接错电源烧了的事情了;再比如所有接口都加上了静电保护,静电耐压值达到12KV,总的说来,用料还是很足的(花了大价钱的....)

IP core可以可以直接使用atlys版的可以通过FPGA直接输出图像,不需要修改。实际上,我的做法是直接使用atlys的工程,然后修改约束文件,生成的mcs可以使用。

如果采用ML605版的IP,则可以通过ASIC输出图像,因为不能把全局时钟直接输出到引脚上,所以需要修改一下dvi_out.vhd这个文件,把dvi_clk_p<=clk;修改成如下ODDR2输出

-- dvi_clk_p<=clk;

ODDR2_inst : ODDR2

generic map(

DDR_ALIGNMENT => "NONE", -- Sets output alignment to "NONE", "C0", "C1"

INIT => '0', -- Sets initial state of the Q output to '0' or '1'

SRTYPE => "SYNC") -- Specifies "SYNC" or "ASYNC" set/reset

port map (

Q => dvi_clk_p, -- 1-bit output data

C0 => clk, -- 1-bit clock input

C1 => not clk, -- 1-bit clock input

CE => '1', -- 1-bit clock enable input

D0 => '1', -- 1-bit data input (associated with C0)

D1 => '0', -- 1-bit data input (associated with C1)

R =>'0', -- 1-bit reset input

S => '0' -- 1-bit set input

);

真是很感谢大家提供的帮助,才能有这次试做的成果。

接下来将把整理后共享,这次试做了5块板子,除了开发调试用外,希望能挤出一块来共大家测试使用,得先确定一个测试负责人,做一个详细一点的计划,包括功能测试、演示,板卡的借用规则等等吧。

先上一幅开发板的照片: