TQ210裸机编程(5)——系统时钟配置

之前都是把程序直接下载到DDR内存,然后直接跳转到内存去运行,之所以可以运行是因为开发板自带的u-boot已经初始化好了DDR内存、时钟等。由于u-boot已经初始化好了时钟,因此这次实验就不能像之前那样操作了,而需要把程序直接烧写到SD卡,然后从SD卡启动。

S5PV210启动流程:

查看S5PV210芯片手册和《S5PV210_iROM_ApplicationNote_Preliminary_20091126》

可以通过配置OM引脚选择如下任意一个设备启动

? General NAND Flash memory

?OneNAND memory

? SD/ MMC memory (such as MoviNAND and iNAND)

?eMMC memory

?eSSD memory

? UART and USB devices

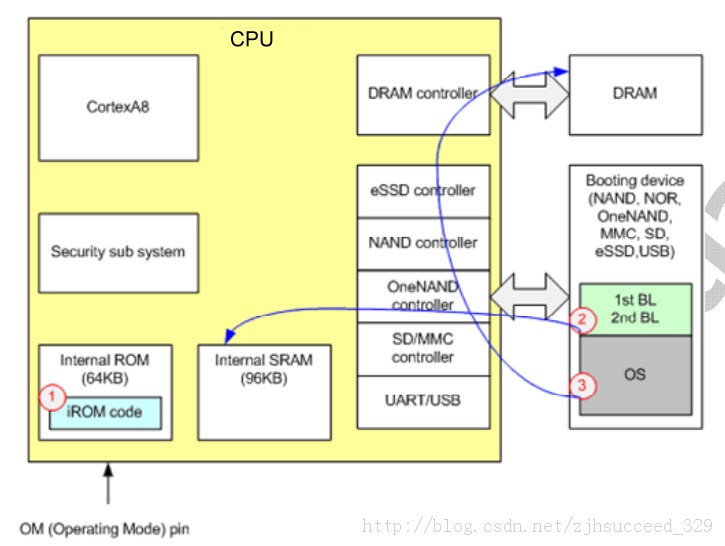

在系统复位时,CPU从固化在片内ROM里的代码开始执行,然而系统复位可能不是在启动时,也可能在被唤醒时,因此IROM Code必须根据复位状态做出适当的处理。

? iROM代码放在片内64KB ROM中。它初始化基本的系统功能,比如时钟,栈,堆。

? iROM代码从从指定的启动设备(NAND/SD/NOR等)加载第1阶段boot loader(BL1)到片内96KB的SRAM。启动设备通过OM引脚选择。

? 第1阶段的boot loader(BL1)加载第2阶段的boot loader(BL2)到片内SRAM

? 第2阶段boot loader(BL2)初始化系统时钟,UART和DRAM控制器。初始化DRAM后,它从启动设备加载操作系统镜像到DRAM。

? 当启动完成后,第2阶段boot loader(BL2)跳转到操作系统去执行。

程序开始于iROM,然后到SRAM,最终程序在DRAM中执行。

iROM(BL0)启动序列如下:

1. 关闭看门狗

2. 初始化指令icache.

3. 初始化栈和堆

4. 初始化块设备拷贝函数

5. 设置时钟分频, 锁定时间, 锁相环(PLL)和时钟源.

6. 检测OM引脚选择从哪个设备启动,然后从启动设备加载BL1(最大16KB)到iRAM

7. 对BL1的校验和进行验证,如果验证失败,iROM将尝试从第2个设备启动

8. 如果是安全模式启动,则对BL1进行完整性验证

9. 跳转到BL1的起始地址(0xD0020010)

iRAM(BL1)启动序列如下:

1. 从启动设备加载BL2(最大80KB)到iRAM

2. 初始化系统时钟,UART,DRAM

3. 从启动设备加载OS到DRAM

4. 跳转到DRAM中的OS执行(0x2000000 或 0x40000000)

iROM在加载BL1时会校验BL1的头信息,规定如下

0x0:BL1的大小(最大16KB - 16B)

0x4 : 0 规定

0x8 : BL1的校验和

0x16 : 0 规定

所以我们在生成led.bin后,还需要添加16B的头信息。

校验和计算方法见《S5PV210_iROM_ApplicationNote_Preliminary_20091126》

SD/MMC拷贝函数,我的判断是:在iROM从SD卡加载BL1时,使用的就是这个函数,注意里面的关键参数

param u16 blockSize : Number of blocks to copy.

拷贝多少块,也就是说在iROM从SD卡加载BL1时是按块的整数倍拷贝的,而不是按字节拷贝。再接着看

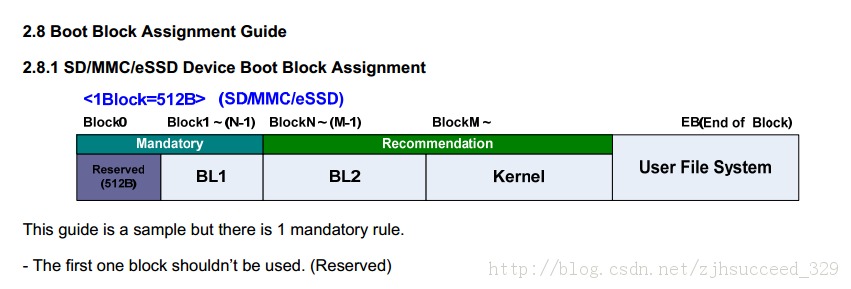

从这可以看出一个块的大小是512字节,而且第0块保留不用,我们需要将led.bin 从第1块开始烧写。

所以BL1的头信息的BL1的大小应该是512的整数倍。我刚开始没有注意到这点,在制作头信息时按led.bin的实际大小(多少字节)来填充第0字节,导致iROM校验失败,没法启动。

时钟配置:

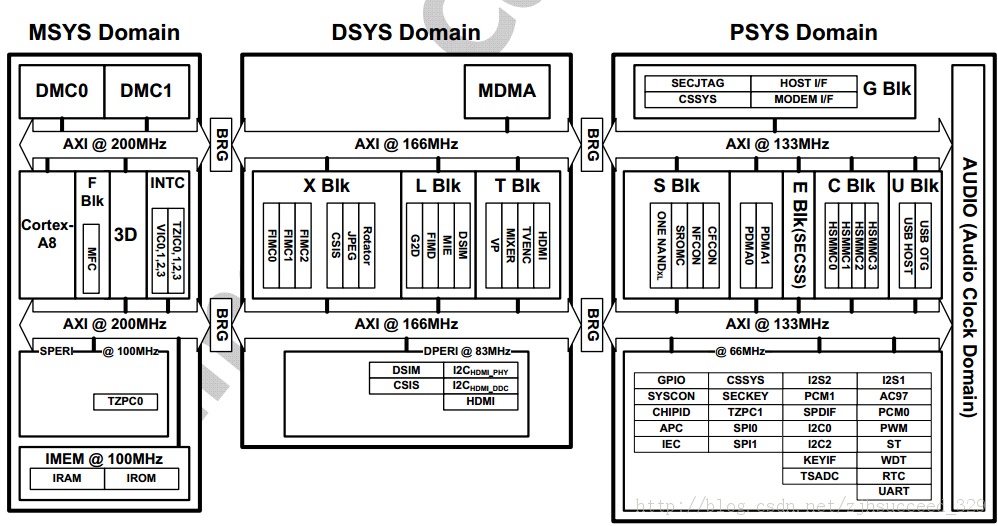

S5PV210由3个时钟域构成,分别是主系统(MSYS),显示系统—SYS),外围系统(PSYS)。

1.MSYS域包括Cortex A8核、DRAM内存控制器、3D、iROM、iRAM、INTC等。

2.DSYS域包括显示相关模块,包括FIMC、FIMD、JPEG等。

3.PSYS域用于安全、I/O外围、低功耗的声音播放等。

如下图所示

S5PV210包含4个锁相环(APLL、MPLL、EPLL、VPLL)

手册上建议使用24MHz的晶振为4个PLL提供输入时钟。

在S5PV210中的典型应用:

? Cortex A8 and MSYS clock domain uses APLL (that is, ARMCLK, HCLK_MSYS, and PCLK_MSYS).

? DSYS and PSYS clock domain (that is, HCLK_DSYS, HCLK_PSYS, PCLK_DSYS, and PCLK_PSYS) and

other peripheral clocks (that is, audio IPs, SPI, and so on) use MPLL and EPLL.

? Video clocks uses VPLL.手册推荐的时钟

?freq(ARMCLK) = 1000 MHz

?freq(HCLK_MSYS) = 200 MHz

?freq(HCLK_IMEM) = 100 MHz

?freq(PCLK_MSYS) = 100 MHz

?freq(HCLK_DSYS) = 166 MHz

?freq(PCLK_DSYS) = 83 MHz

?freq(HCLK_PSYS) = 133 MHz

?freq(PCLK_PSYS) = 66 MHz

? freq(SCLK_ONENAND) = 133 MHz, 166 MHzPLL:

? APLL 用来驱动 MSYS 域 和 DSYS 域. 它能产生高达 1 GHz的频率

? MPLL用来驱动 MSYS 域和 DSYS 域.它能产生高达 2 GHz的频率

? EPLL 主要用来产生 声音相关的时钟.

? VPLL主要用来产生视频系统操作的时钟, 54 MHz.

? 典型的, APLL 驱动MSYS域,MPLL 驱动DSYS 域.时钟配置步骤如下:

Turn on a PLL

(A,M,E,V)PLL_CON[31] = 1; // Power on a PLL (Refer to (A, M, E, V) PLL_CON SFR)wait_lock_time; // Wait until the PLL is locked

(A, M, E, V)PLL_SEL = 1; // Select the PLL output clock instead of input reference clock, after PLL

output clock is stabilized. (Refer to 0, 4, 8, 12th bit of CLK_SRC0 SFR)Once you turned on any PLL, do not turn off that.

Change PLL’s PMS values

Set PMS values; // Set PDIV, MDIV, and SDIV values

(Refer to (A, M, E, V) PLL_CON SFR)Change the system clock divider values

CLK_DIV0 [31:0] = target value0;Change the divider values for special clocks

CLK_DIV1 [31:0] = target value1;

CLK_DIV2 [31:0] = target value2;代码如下:

start.S

clock.c

然后上电可以看到LED交替闪烁,可以去掉start.S中的时钟初始化,再次编译程序,烧写,可以看出LED闪烁变慢了。

.global _start/* 声明一个全局的标号 */_start://bl clock_init/* 时钟初始化 */bl main/* 跳转到C函数去执行 */halt:b halt